Sci(entific)-Compiler is a Nuclear Instruments software designed to accelerate the implementation of firmware for signal processing in scientific instrumentation. The software is targeted to generate custom applications for nuclear physics world. For example it is possible to implement:

- Complex trigger logic

- Event Counters

- Single Channel (SCA) and Multi Channel Analyzer (MCA)

- Time to Digital Converter

- Replacement for any old digital NIM module logic based system

- Time tagging logic

- Wave digitizer

- Logic Analyzer

- Read out of both digital and analog ASICs

All these applications require high computational power. For example, to implement an MCA the processing system should be able to analyze any sample captured by an ADC at a rate of about 100 MHz and apply on them the following operations:

- Trigger to separate the signal from the noise

- Exponential de-convolution (to remove the exponential shape of the preamplifier)

- Energy calculation convolving the data stream with an optimum filter (i.e. a trapezoidal filter)

- Baseline estimation and subtraction

Al these operations require at least 10 GFLOPS (10 billion of operation per seconds) and could not be performed in realtime even by a powerful computer.

A typical solution consists in exploit a high parallel device to implement several processing cores to divide the problem in smaller sub-problems and compute them in parallel.

FPGA (Field Programmable Gate Array) devices consist in a large configurable logic matrix that could be configured to implement any logic function. Inside an FPGA device there are several configurable logic tables, memory cells, large memory areas, arithmetic processing units, communication blocks and a large interconnection matrix that is used to interconnect all internal resources. Configuring the different FPGA resources, the system developer is able to implement not only logic function but also complex processing algorithm exploiting both the data (pipeline processing) and control (sequential processing) paths.

FPGA designs are much more similar to electronic circuit then to a standard software or firmware.

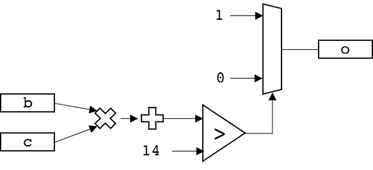

It is possible for example to implement the algorithm

a = b*c+5;

if (a>14) o=1; else o=0;

but it is translated in a digital circuit that implements all the processing core

In the FPGA device it will be physically implemented:

- 1 multiplier

- 1 full adder

- 1 comparator

- 1 multiplexer

In a classical CPU there is one processing core (ALU) that executes a software instruction by instruction always using the same peace of hardware which function is selected by the instruction to be processed.

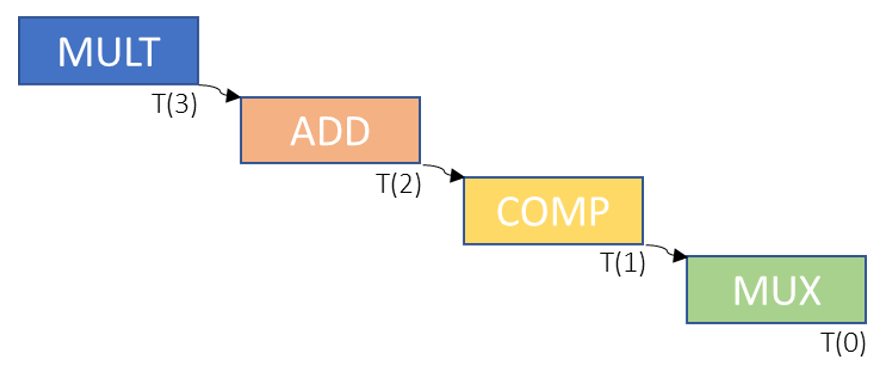

It should be clear that the FPGA solution allows a significant increment in the processing performance: the multiplier, the adder, the comparator and the multiplexer operate at the same time processing the data in a 4 stages pipeline. The circuit is able to generate an output sample for each clock cycle.

Writing algorithm for FPGA is not a simple task: not only the typical programming languages (VHDL/Verilog) are not easy to learn but also the developer should be able to transform the step by step algorithm in a physical circuit. Moreover, the circuit will work on a real hardware that has limitations in terms of available resources (number of logic element, arithmetic core, quantity of memory) and in terms of speed. All logic elements and nets introduce a propagation delay that limits the maximum operating speed.

Sci-Compiler is an innovative software that simplifies all programming step allowing everyone with few technical skills to implement any complex processing system. Sci-Compiler allows the design of a full system using graphical interconnection of prebuilt processing blocks. The processing blocks are organized in libraries and implement complex functions like charge integration, trapezoidal filtering, trigger, spectrum, …

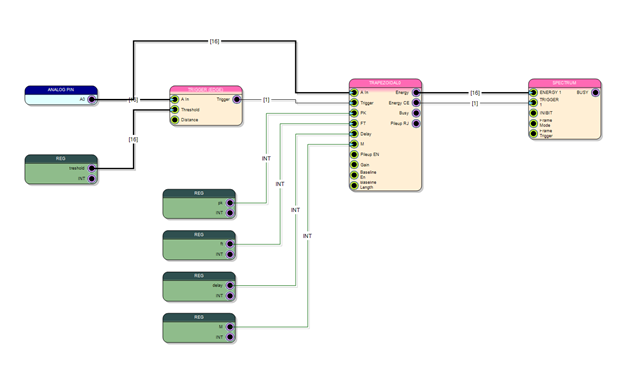

For example, to implement an MCA on the CAEN DT5550 that generates in output a 1024 channels spectrum for each channel the user should implement a design block like this:

The trigger and the spectrum parameters can be configured by the PC accessing to the register (Green Block).

Sci-Compiler generates in output both the FPGA bitstream and the C library and a C example to interact with the design compiling it in Windows (Visual Studio), Linux (gcc) and MACOS (Xcode).

For example the library generated for the previous circuit will export the following functions:

SCILIB int REG_threshold_SET(uint32_t val, int32_t handle);

SCILIB int REG_pk_SET(uint32_t val, int32_t handle);

SCILIB int REG_ft_SET(uint32_t val, int32_t handle);

SCILIB int REG_M_SET(uint32_t val, int32_t handle);

SCILIB int REG_delay_SET(uint32_t val, int32_t handle);

SCILIB int MMC_spectrum_SP0_INTEGRAL_GET(uint32_t *val, int32_t handle);

SCILIB int MMC_spectrum_SP0_PARTIAL_GET(uint32_t *val, int32_t handle);

The first five functions configure the trigger threshold, the trapezoidal peaking time, flat top, de-convolution parameter and sampling delay. The last two instructions return the accumulated spectrum and the partial (from last readout) spectrum.

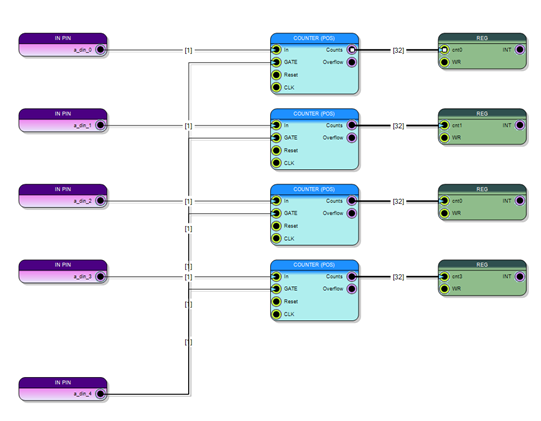

The following circuit implements a 4 channel counter read out by usb/ethernet/VME that could be implemented on the Caen V2495.

There are 4 input signals connected to the counter inputs and a GATE signal that could be used to inhibit the counting. The counting outputs are connected to four memory mapped registers. The software generates the V2495 bitstream and a C library that exports these functions:

SCILIB int REG_cnt0_GET(uint32_t *val, int32_t handle);

SCILIB int REG_cnt1_GET(uint32_t *val, int32_t handle);

SCILIB int REG_cnt2_GET(uint32_t *val, int32_t handle);

SCILIB int REG_cnt3_GET(uint32_t *val, int32_t handle);

Those functions can be used to read the counters value from the PC.

Sci-Compiler has a large library function set that significantly simplifies the design of processing system minimizing the time to develop the final application, reducing to zero the learning curve and reducing the design error thanks to the certified Nuclear Instruments FPGA Libraries.

Sci-Compiler is not just a schematic based programming language like Xilinx Vivado Design Block or Altera Schematic Entry. The schematic blocks are not simply logic function or flip flop but complex macro-blocks that implement complete instruments functionalities to measure amplitude, energy, time of arrival of incoming signals. Moreover, Sci-Compiler generates all the code necessary to implement the communication interface between the implemented design and the computer. It supports the following communication bus: USB3, USB2, Ethernet and VME.

Nuclear Instruments Sci-Compiler fully supports the following hardware devices developed by Caen and Nuclear Instruments:

- V2495 Programmable Logic Unit

- DT5550 Programmable pulse processing and readout system